# UNIVERSIDADE FEDERAL DE SERGIPE CENTRO DE CIÊNCIAS EXATAS E TECNOLÓGICAS PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

Paralelização em CUDA do Algoritmo Aho-Corasick Utilizando as Hierarquias de Memórias da GPU e Nova Compactação da Tabela de Transição de Estados

José Bonifácio da Silva Júnior

UNIVERSIDADE FEDERAL DE SERGIPE

CENTRO DE CIÊNCIAS EXATAS E TECNOLÓGICAS

PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA

COMPUTAÇÃO

José Bonifácio da Silva Júnior

Paralelização em CUDA do Algoritmo Aho-Corasick Utilizando as Hierarquias de Memórias da GPU e Nova Compactação da Tabela de Transição de Estados

**Dissertação** apresentada ao Programa de Pós-Graduação em Ciência da Computação (PROCC) da Universidade Federal de Sergipe (UFS) como parte de requisito para obtenção do título de Mestre em Ciência da Computação.

Orientador: Prof. Dr. Edward David Moreno Ordonez

SÃO CRISTÓVÃO/SE

2017

#### José Bonifácio da Silva Júnior

# Paralelização em CUDA do Algoritmo Aho-Corasick Utilizando as Hierarquias de Memórias da GPU e Nova Compactação da Tabela de Transição de Estados

**Dissertação** apresentada ao Programa de Pós-Graduação em Ciência da Computação (PROCC) da Universidade Federal de Sergipe (UFS) como parte de requisito para obtenção do título de Mestre em Ciência da Computação.

## **BANCA EXAMINADORA**

Prof. Dr. Edward David Moreno Ordonez, Orientador Universidade Federal de Sergipe (UFS)

Prof. Dr. Ricardo José Paiva de Britto Salgueiro Universidade Federal de Sergipe (UFS)

> Prof. Dr. Ricardo dos Santos Ferreira Universidade Federal de Viçosa (UFV)

# Paralelização em CUDA do Algoritmo Aho-Corasick Utilizando as Hierarquias de Memórias da GPU e Nova Compactação da Tabela de Transição de Estados

Este exemplar corresponde à Dissertação de Mestrado, sendo o Exame de Defesa do mestrando **JOSÉ BONIFÁCIO DA SILVA JÚNIOR** para ser aprovada pela Banca Examinadora.

São Cristóvão – SE, 21 de Junho de 2017

Prof. Dr. Edward David Moreno Ordonez,

Orientador, UFS

Prof. Dr. Ricardo José Paiva de Britto Salgueiro, Examinador, UFS

Prof. Dr. Ricardo dos Santos Ferreira,

Examinador, UFV

Júnior, José Bonifácio da Silva.

Paralelização em CUDA do Algoritmo Aho-Corasick Utilizando as Hierarquias de Memórias da GPU e Nova Compactação da Tabela de Transição de Estados / José Bonifácio da Silva Júnior; orientador Edward David Moreno Ordonez. — São Cristovão, 2017. 71f.;

Dissertação (Mestrado em Ciência da Computação) – Universidade Federal de Sergipe, 2017.

1. Computação de alto desempenho. 2. Arquitetura de Computadores. 3. Segurança da Informação. I. Ordonez, Edward David Moreno, orientador. II. Paralelização em CUDA do Algoritmo Aho-Corasick Utilizando as Hierarquias de Memórias da GPU e Nova Compactação da Tabela de Transição de Estados.

#### **AGRADECIMENTOS**

Agradeço primeiramente a Deus, pois Ele mais uma vez me deu a força necessária para vencer mais uma grande batalha da minha vida. Agradeço aos meus pais, Maria de Fátima Costa Silva e José Bonifácio da Silva, por me darem todo carinho e suporte necessários e por muitas vezes me compreederem com a paciência que apenas os pais e as pessoas que nos amam têm.

Agradeço ao professor Dr. Ricardo Salgueiro por fazer parte da minha banca de defesa do mestrado, mas, acima disso, pelo grande professor e ser humano que é (acho que é a pessoa mais feliz que conheço, nunca o vi de mau humor). Obrigado por ter me passado de forma clara e de fácil compreensão conhecimentos ainda na graduação em uma das áreas que mais gosto que é a área de segurança de redes. Isso me influenciou fortemente a dar continuidade nos estudos da área. Além disso, viabilizou a parceria com o Laboratório de Computação de Alto Desempenho – LCAD – da UFS, que possibilitou que eu realizasse os experimentos desta dissertação.

Agradeço ao professor Dr. Ricardo Ferreira, membro externo da banca, mas que (apesar de externo) me auxiliou "de perto" neste trabalho, sempre sendo solicito demais, respondendo às várias dúvidas que surgiram durante o trabalho em uma velocidade que mostrava o interesse dele em ajudar e passar o conhecimento sobre as GPUs. Foi essencial para o meu aprendizado na área de paralelização de algoritmos com GPUs ao ministrar o curso presencial da NVIDIA e a partir daí fazer surgir boas idéias para serem apicadas neste trabalho. Além disso, também viabilizou a parceria com a Universidade Federal de Viçosa (UFV), ao possibilitar que eu realizasse os experimentos em uma das GPUs dessa universidade.

Agradeço de forma especial ao meu orientador professor Dr. Edward Moreno por ter me acompanhado de perto neste desafio e pela competência de ter me mostrado os melhores caminhos para que eu concluísse com êxito este trabalho. Obrigado pela parceria e confiança, pela busca incansável das melhores soluções e também por ter sugerido que eu fizesse o mestrado ainda quando eu estava na graduação.

Agradeço aos meus irmãos Thiago, Danilo e Fábio que me ajudaram bastante nesta caminhada, meus familiares e minha namorada Ana Cristina, a qual esteve comigo não só nos bons momentos, mas também nos momentos que mais precisei de forças para continuar. Agradeço aos meus colegas e já amigos da equipe de TI da Corregedoria do Tribunal de Justiça de Sergipe pelos incentivos dados para que eu concluísse este trabalho e não desistisse em momento algum. Agradeço a todos os outros amigos, os que atualmente estão mais próximos como Marcelo, Marco e Nelmo e todos os outros que devido aos caminhos que a vida reserva para cada um de nós estão mais distantes fisicamente, mas que fazem parte da minha história.

Por fim agradeço a todos os professores da Universidade Federal de Sergipe, em especial aos professores do departamento de Ciência da Computação, por me concederem os conhecimentos que complementaram a minha formação de Mestre em Ciência da Computação.

# Lista de Figuras

| Figura 2.1: Exemplo de regra disponível no site do Snort                                        | 14  |

|-------------------------------------------------------------------------------------------------|-----|

| Figura 2.2: Fluxograma de execução do Snort (Junta e Pereira, 2015)                             | 15  |

| Figura 2.3: Percentual do tempo de execução dos trechos do componente de detecção (Junta e      |     |

| Pereira, 2015)                                                                                  | 16  |

| Figura 2.4: Ilustração de uma arquitetura heterogênea com CPU e GPU (CHENG, et al., 2014)       | 17  |

| Figura 2.5: Comparação entra as arquiteturas Fermi e Kepler (CHENG, et al., 2014)               | 18  |

| Figura 2.6: Visão lógica x visão de hardware da programação em CUDA                             | 19  |

| Figura 2.7: Arquitetura geral de uma GPU (Tran, et al., 2012)                                   | 20  |

| Figura 2.8: Ilustração do Naive Puro (à esquerda) e do Naive Melhorado (à direita) (DAN, 1997)  | 23  |

| Figura 2.9: Construção do grafo goto (AHO e CORASICK, 1975)                                     | 24  |

| Figura 2.10: Funções usadas no algoritmo AC (Tran, et al., 2012)                                | 25  |

| Figura 2.11: Algoritmo PFAC (LIN et al., 2013).                                                 | 26  |

| Figura 2.12: Exemplo do PFAC para os padrões "AB", "ABG", "BEDE", e "ED" (LIN et al., 2013)     | 27  |

| Figura 2.13: Comparação das taxas de transferências com pacotes DEFCON de tamanhos diferent     |     |

| (LIN et al., 2013)                                                                              | 28  |

| Figura 2.14: Ilustração da Tabela de Transição de Estado (TRAN et al., 2012)                    | 29  |

| Figura 2.15: Ilustração da abordagem de memória global (TRAN et al., 2012)                      | 30  |

| Figura 2.16: Ilustração da abordagem de memória compartilhada (TRAN et al., 2012)               | 30  |

| Figura 2.17: Resultado das três abordagens usando 1000 padrões (TRAN et al., 2012)              | 31  |

| Figura 2.18: Comparação das velocidades (TRAN et al., 2012)                                     | 31  |

| Figura 2.19: Resultado das três abordagens para 200 MB de texto de entrada (TRAN et al., 2012)  | 32  |

| Figura 2.20: CPU e GPU com Aho-Corasick (Thambawita et al., 2014)                               | 33  |

| (2014, Higura 2.21: Ilustração do bitmap correspondente ao primeiro nó de um DFA (BELLEKENS     | 36  |

| Figura 3.1: Etapas da pesquisa                                                                  | 37  |

| Figura 4.1: Ilustração do processamentos dos softwares                                          | 40  |

| Figura 4.2: Fluxograma da função main de todos os algoritmos desenvolvidos nos testes iniciais  | 41  |

| Figura 4.3: Pseudocódigo base para os experimentos com o Naive                                  | 42  |

| Figura 4.4: Trecho do pseudocódigo da abordagem 1 do Naive paralelo                             | 44  |

| Figura 4.5: Trecho do pseudocódigo da abordagem 3 do Naive paralelo                             | 44  |

| Figura 4.6: Resultados experimentais das abordagens do Naive                                    | 45  |

| Figura 4.7: Pseudocódigo da primeira abordagem do Aho-Corasick paralelo                         | 46  |

| Figura 4.8: Resultados experimentais das abordagens do Aho-Corasick                             | 46  |

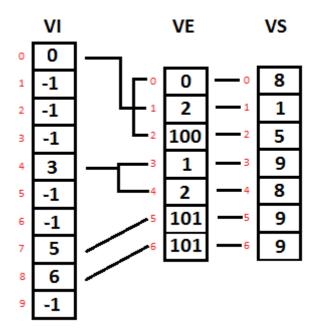

| Figura 4.9: Tabela de Transição de Estados (Adaptada de TRAN et al., 2013)                      | 47  |

| Figura 4.10: STT compactada                                                                     | 48  |

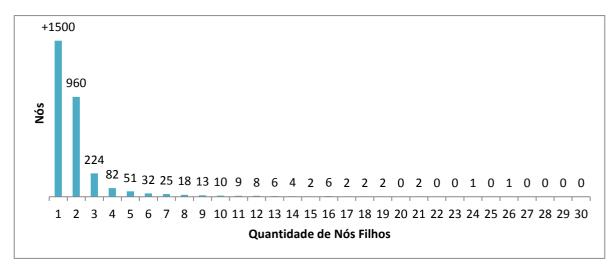

| Figura 4.11: Quantidade de nós filhos em uma máquina real                                       | 50  |

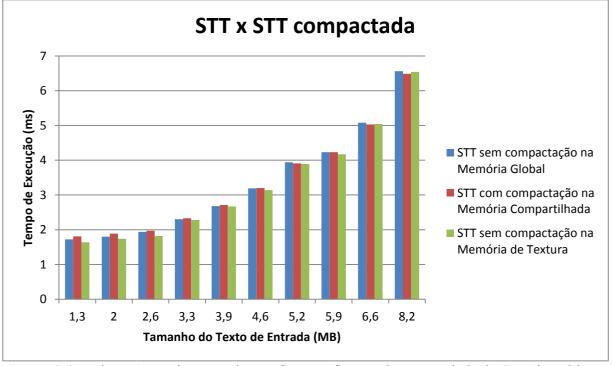

| Figura 4.12: Curva de crescimento dos tempos de execução nas versões normal e compactada do     |     |

| Aho-Corasick paralelo                                                                           | 51  |

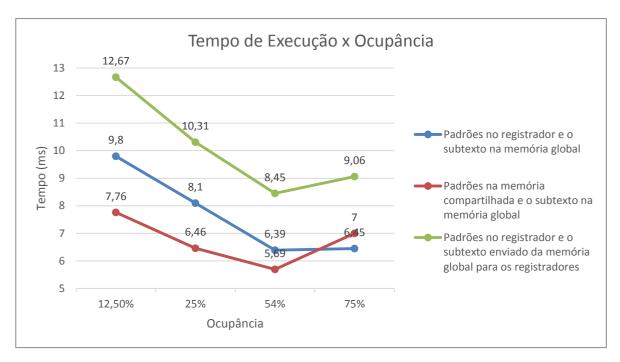

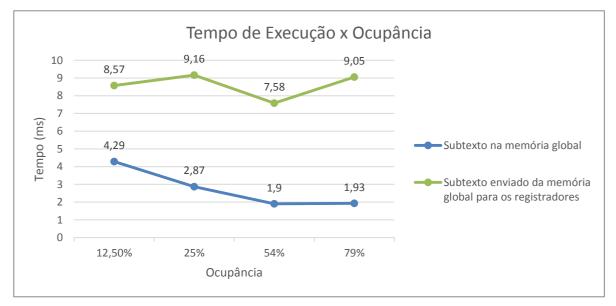

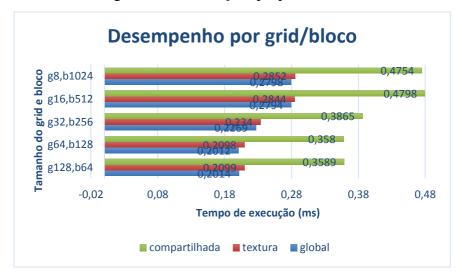

| Figura 5.1: Variação do tamanho do grid e bloco da GPU                                          | 54  |

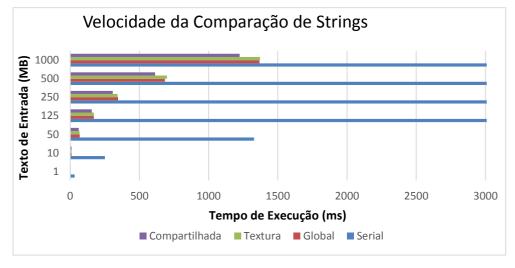

| Figura 5.2: Tempo de execução das quarto abordagens                                             | 55  |

| Figura 5.3: Tempo de execução das quatro metodologias na placa Tesla K20                        | 56  |

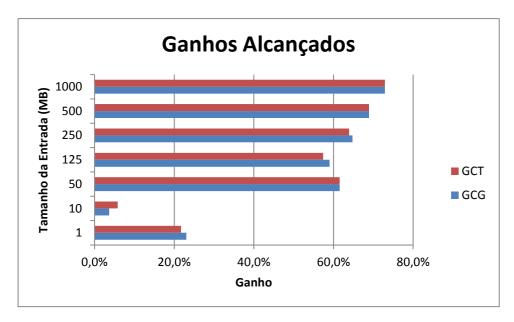

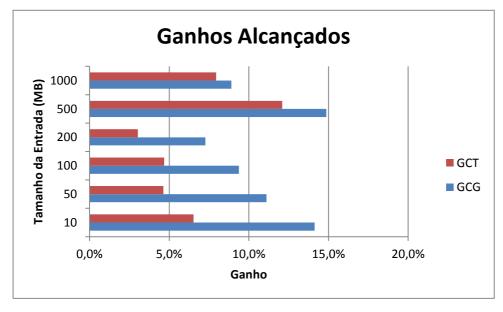

| Figura 5.4: Ganhos obtidos com a abordagem compartilhada utilizando dados sintéticos - Tesla K2 | 20. |

|                                                                                                 | 57  |

| Figura 5.5: Tempo de execução das quatro metodologias na placa Titanx                           | 58  |

| . Figura 5.6: Ganhos obtidos com a abordagem compartilhada utilizando dados sintéticos - Titanx | 59  |

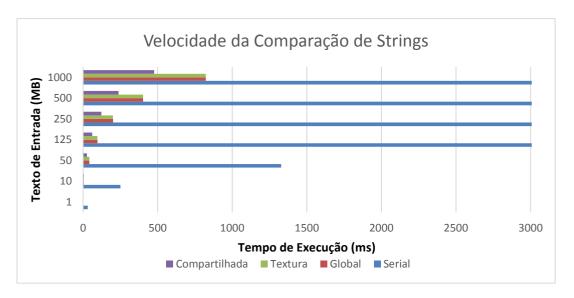

| Figura 5.7: Tempo de execução das quatro metodologias na placa Tesla K20 – dados reais          |     |

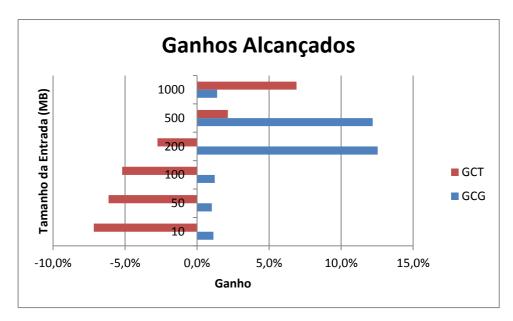

| Figura 5.8: Ganhos obtidos com a abordagem compartilhada utilizando dados reais - Tesla K20     | 60  |

| Figura 5.9: Tempo de execução das quatro metodologias na placa Titanx – dados reais             |     |

| Figura 5.10: Ganhos obtidos com a abordagem compartilhada utilizando dados reais - Titanx       | 61  |

| Figura 6.1: Trecho do código da função goto                                                     | 68  |

| Figura 6.2: Trecho do código da função de falha                                                 | 68  |

| Figura 6.3: Trecho do código da função output                                                   | 68  |

# Lista de Tabelas

| Tabela 4.1: Redução da quantidade de dados através da compactação     | 50 |

|-----------------------------------------------------------------------|----|

| Tabela 5.1: Taxa de transferência (Mcps)                              |    |

| Tabela 5.2: Resultados experimentais com dados sintéticos - Tesla K20 |    |

| Tabela 5.3: Resultados experimentais com dados sintéticos - Titanx    | 58 |

| Tabela 5.4: Resultados experimentais com dados reais – Tesla K20      | 60 |

| Tabela 5.5: Resultados experimentais com dados reais – Titanx         | 61 |

# Sumário

| 1. | Introduç   | ão                                                      | 10 |  |  |

|----|------------|---------------------------------------------------------|----|--|--|

|    | 1.1. N     | 1otivação                                               | 10 |  |  |

|    | 1.2. O     | bjetivos da Dissertação                                 | 12 |  |  |

|    | 1.2.1.     | Objetivos Específicos                                   | 12 |  |  |

|    | 1.3. O     | rganização do Trabalho                                  | 12 |  |  |

| 2. | Snort, GF  | PUs e Algoritmos de Comparação de Strings               | 14 |  |  |

|    | 2.1. Si    | nort                                                    | 14 |  |  |

|    | 2.2. U     | nidade de Processamento Gráfico (GPU)                   | 16 |  |  |

|    | 2.3. A     | lgoritmos de Comparação de Strings                      | 21 |  |  |

|    | 2.3.1.     | Naive (Força-Bruta)                                     | 22 |  |  |

|    | 2.3.2.     | Aho-Corasick                                            | 23 |  |  |

|    | 2.4. Es    | stado da Arte                                           | 26 |  |  |

|    | 2.4.1.     | Algoritmo Paralelo PFAC                                 | 26 |  |  |

|    | 2.4.2.     | Memórias Compartilhadas e Caches de Textura da GPU      | 28 |  |  |

|    | 2.4.3.     | GPU x CPU                                               | 32 |  |  |

|    | 2.4.4.     | Paralelização de vários Algoritmos                      | 33 |  |  |

|    | 2.4.5.     | Mapeamento Sistemático do Algoritmo AC paralelo         | 34 |  |  |

|    | 2.4.6.     | A técnica de compactação por Bit-mapeamento             | 35 |  |  |

|    | 2.5. C     | onsiderações Finais do Capítulo                         | 36 |  |  |

| 3. | Metodol    | ogia da Pesquisa                                        | 37 |  |  |

|    | 3.1. N     | lateriais e Métodos                                     | 37 |  |  |

| 4. | Paraleliza | ação Inicial e Compactação do Aho-Corasick              | 40 |  |  |

|    | 4.1. C     | omunicação CPU - GPU                                    | 40 |  |  |

|    | 4.2. N     | aive Puro e Melhorado                                   | 42 |  |  |

|    | 4.3. A     | ho-Corasick Paralelo                                    | 45 |  |  |

|    | 4.4. P     | roposta e uso de uma nova técnica de compactação da STT | 47 |  |  |

| 5. | Resultad   | os GPU x CPU                                            | 53 |  |  |

|    | 5.1. A     | nálise com Pacotes Sintéticos                           | 54 |  |  |

|    | 5.1.1.     | TESTE 1 – Bloco de Tamanho 1024                         | 54 |  |  |

|    | 5.1.2.     | 1.2. TESTE 2 – Blocos de Tamanho 100 e 1000             |    |  |  |

|    | 5.2. A     | nálise com Pacotes Reais                                | 59 |  |  |

| 6  | Conclusã   |                                                         | 63 |  |  |

#### **RESUMO**

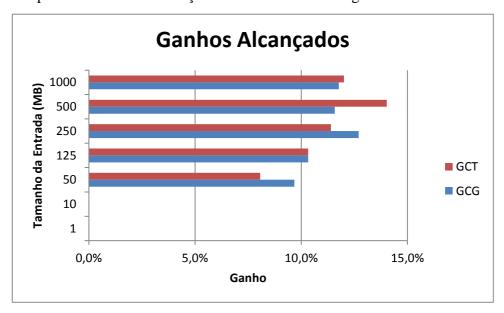

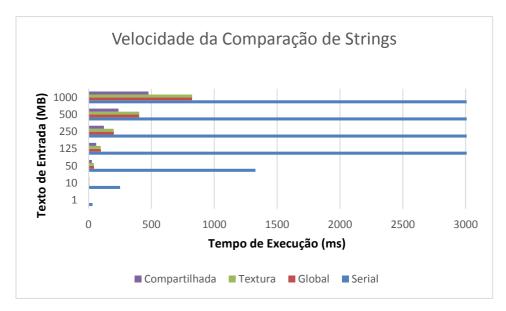

Um Sistema de Detecção de Intrusão (IDS) necessita comparar o conteúdo de todos os pacotes que chegam na interface da rede com um conjunto de assinaturas que indicam possíveis ataques, tarefa esta que consome bastante tempo de processamento da CPU. Para amenizar esse problema, tem-se tentado paralelizar o motor de comparação dos IDSs transferindo sua execução da CPU para a GPU. Esta dissertação tem como objetivo fazer a paralelização dos algoritmos de comparação de strings Força-Bruta e Aho-Corasick e propor uma nova compactação da Tabela de Transição de Estados do algoritmo Aho-Corasick a fim de possibilitar o uso dela na memória compartilhada e acelerar a comparação de strings. Os dois algoritmos foram paralelizados utilizando a plataforma CUDA da NVIDIA e executados nas memórias da GPU a fim de possibilitar uma análise comparativa de desempenho dessas memórias. Inicialmente, o algoritmo AC mostrou-se mais veloz do que o algoritmo Força-Bruta e por isso seguiu-se para sua otimização. O algoritmo AC foi compactado e executado de forma paralela na memória compartilhada, alcançando um ganho de desempenho de 15% em relação às outras memórias da GPU e sendo 48 vezes mais rápido que sua versão na CPU quando os testes foram feitos com pacotes de redes reais. Já quando os testes foram feitos com dados sintéticos (dados menos aleatórios) o ganho chegou a 73% e o algoritmo paralelo chegou a ser 56 vezes mais rápido que sua versão serial. Com isso, pode-se perceber que o uso da compactação na memória compartilhada torna-se uma solução adequada para acelerar o processamento de IDSs que necessitem de agilidade na busca por padrões.

**Palavras-chaves:** GPUS, CUDA, Algoritmos de Comparação de *Strings*, Aho-Corasick, IDS, Hierárquia de Memória da GPU, Técnicas de Compactação.

#### **ABSTRACT**

The Intrusion Detection System (IDS) needs to compare the contents of all packets arriving at the network interface with a set of signatures for indicating possible attacks, a task that consumes much CPU processing time. In order to alleviate this problem, some researchers have tried to parallelize the IDS's comparison engine, transferring execution from the CPU to GPU. This This dissertation aims to parallelize the Brute Force and Aho-Corasick string matching algorithms and to propose a new compression of the State Transition Table of the Aho-Corasick algorithm in order to make it possible to use it in shared memory and accelerate the comparison of strings. The two algorithms were parallelized using the NVIDIA CUDA platform and executed in the GPU memories to allow a comparative analysis of the performance of these memories. Initially, the AC algorithm proved to be faster than the Brute Force algorithm and so it was followed for optimization. The AC algorithm was compressed and executed in parallel in shared memory, achieving a performance gain of 15% over other GPU memories and being 48 times faster than its serial version when testing with real network packets. When the tests were done with synthetic data (less random data) the gain reached 73% and the parallel algorithm was 56 times faster than its serial version. Thus, it can be seen that the use of compression in shared memory becomes a suitable solution to accelerate the processing of IDSs that need agility in the search for patterns.

**Keywords:** GPUS, CUDA, string matching algorithms, Aho-Corasick, IDS, GPU Memory Hierarchy, Compaction Techniques.

# 1. Introdução

A tecnologia da informação (TI) tem sido cada vez mais determinante para o sucesso de empresas e organizações ao redor do mundo e possui as redes de computadores como um dos seus principais meios de transmissão de dados. Juntamente com o aumento da importância da TI, cresceu também a necessidade de proteção do seu maior patrimônio, a informação.

Para combater o acesso não autorizado aos sistemas de TI ou falhas ocasionadas por ataques de *hackers*, os profissionais da área de segurança da informação utilizam várias ferramentas, cada uma com função específica. Uma dessas ferramentas é o IDS (*Intrusion Detection System*), que tem a finalidade de detectar uma série de ataques na rede.

O IDS é uma ferramenta que analisa as atividades do sistema e da rede para verificar possíveis ataques, se possível em tempo real. Ele faz a coleta de informações sobre os pacotes que circulam na rede e verifica a existência de ataques conhecidos como vírus, worms, spyware ou código malicioso (JAISWAL, 2014).

Um dos IDSs mais utilizados é o Snort, um software *open source* para UNIX e Windows. O Snort é capaz de detectar quando um ataque está sendo realizado e, baseado nas caraterísticas do ataque, alterar ou remodelar sua configuração de acordo com as necessidades e alertar ao administrador do ambiente sobre esse ataque (SANTOS, 2005). O objetivo dele é monitorar o tráfego da rede pacote a pacote em tempo real para verificar se o pacote que chega na interface coincide com algumas das suas assinaturas de ataques préconfiguradas. Em outras palavras, o Snort precisa manipular computacionalmente intensas operações de comparação de *strings*, onde uma grande quantidade de dados precisa ser comparada com suas assinaturas (OKE e VAIDYA, 2015). Esta atividade é bastante custosa para a CPU e, por isso, várias pesquisas de como acelerá-la estão sendo feitas e uma solução que tem ganhado força é a paralelização dos algoritmos que fazem a comparação de *strings* (ou comparação de padrões).

# 1.1. Motivação

Os IDSs, em geral, possuem duas limitações críticas que fazem diminuir sua velocidade de processamento. A primeira é a limitação de entrada e saída causada pelo *overhead* de leitura de pacotes na interface de rede (JACOB e BRODLEY, 2006). A segunda limitação fica por conta das operações de comparação do *payload* do pacote com a coleção de assinaturas, as quais consomem cerca de 70% a 80% do tempo de processamento da CPU

(JAISWAL, 2014). Esses dois problemas poderão causar uma perda considerável de pacotes ou até mesmo derrubar o *host* onde ele está instalado, ferindo dois príncipios básicos da Segurança da Informação que são a integridade e disponibilidade. Perder dados ou tornar o *host* responsável por manter a segurança de uma rede indisponível pode ser intolerável a depender da situação.

Esse cenário tende a ficar cada vez pior uma vez que novos ataques vêm sugindo, necessitando de novos padrões e, consequentemente, aumentando a quantidade de dados para serem comparados. Além disso, as redes estão atingindo níveis de velocidades cada vez maiores, necessitando de algoritmos mais velozes. Os algoritmos tradicionais não conseguem manipular essa grande quantidade de dados em uma velocidade aceitável, chegando ao ponto de tornarem-se inadequados para essa tarefa (OKE e VAIDYA, 2015). E como já foi mencionado anteriormente, a comparação consome cerca de 70% a 80% de todo processamento do Snort, sendo considerada a operação mais crítica do mesmo.

A limitação de *overhead* não parece ser um bom problema para tentar uma aceleração inicialmente, já que chegariam mais pacotes para o Snort processar e criaria-se um gargalo computacional devido à limitação da comparação de *strings*. Já a aceleração desta última mostra-se mais capaz de aumentar o desempenho do Snort, já que não há identificação de outra atividade lenta que utilize os resultados da comparação de *strings*.

O uso das Unidades de Processamento Gráfico (GPUs) é vista como uma solução adequada para acelerar o processamento da comparação de *strings* do Snort, uma vez que as GPUs têm um maior poder de computação do que as CPUs, como pode ser visto em alguns trabalhos como o de LIN, C. et al. (2013) que paralelizaram o algoritmo de comparação de *string* Aho-Corasick (AC) e alcançaram uma velocidade 74,95 vezes maior que a versão serial do mesmo algoritmo e no trabalho de TRAN, N. et al. (2012) que também paralelizaram o algoritmo AC e obtiveram uma melhoria de 15,72 vezes na velocidade de comparação de *strings* em relação à versão serial. Já o trabalho de THAMBAWITA, D. et al. (2014) mostrou que se o texto onde serão procurados os padrões for maior que 40000 bytes (o que tende a acontecer quando um *host* IDS é colocado em uma rede de alta velocidade) o desempenho da GPU supera o da CPU. Por fim, Kouzinopoulos e Margaritis (2008) paralelizaram vários algoritmos de comparação de *strings* obtendo uma melhora de 20 vezes do algoritmo Boyer-Moore-Horspool e, posteriormente, ao usar a memória compartilhada da GPU, aumentou mais 24 vezes essa velocidade.

Outros autores também paralelizaram esses algoritmos, porém usando outras tecnologias, como Jiang, Salamatian e Mathy (2013) que exploraram o grande poder

computacional do processador de múltiplo núcleo TILERAGX36 PCIe, um processador com 36 núcleos desenvolvido pela Tilera Inc e instalado em um servidor x86 com sistema operacional Linux, tendo destacado como melhor resultado o fato do protótipo completo ter exibido velocidade quase linear e pôde suportar até 7,2 Gbps de tráfego com pacotes de 100 bytes. Huang, N. et al. (2008) desenvolveram o PixelSnort, que faz a comparação usando o algoritmo Knuth-Morris-Pratt paralelizado em uma GPU e sendo executado através de chamadas OpenGl no código fonte do Snort. Neste trabalho, o pixelSnort superou o Snort convencional em 40%.

Como se observa há uma tendência em paralelizar algoritmos de comparação de *strings* tradicionais, principalmente quando a tarefa deles é buscar padrões em grandes quantidades de dados, como ocorre no Snort.

# 1.2. Objetivos da Dissertação

O objetivo principal desta dissertação de mestrado é paralelizar algoritmos de comparação de *strings* tradicionais através de GPUs usando a linguagem de programação C na plataforma de computação paralela CUDA. Após paralelizar os algoritmos, acelerar o tempo de execução deles fazendo o uso da memória compartilhada das GPUs através de uma nova técnica de compactação.

## 1.2.1. Objetivos Específicos

Para alcançar o objetivo primário, alguns objetivos específicos têm que ser atendidos, a saber:

- Fazer um estudo na literatura sobre a paralelização do algoritmo de comparação de strings do Snort, o Aho-Corasick;

- Compactar a máquina de estados do Aho-Corasick a fim de possibilitar que o algoritmo seja executado na memória compartilhada da GPU;

- Paralelizar o algoritmo em uma GPU fazendo versões nas memórias global, de textura e compartilhada;

- Comparar o desempenho dos algoritmos paralelizados, além de compará-los com a versão serial do algoritmo;

# 1.3. Organização do Trabalho

A seção 2 apresenta uma breve revisão bibliográfica fazendo uma abordagem sobre o IDS Snort na primeira subseção. A segunda subseção detalha as características de uma GPU genérica, dispositivo necessário para a parelização dos algoritmos. A terceira subseção traz

alguns algoritmos de comparação de *strings* que foram paralelizados e poderão ser utilizados no Snort em substituição aos algoritmos seriais que nele estão. Por fim, a quarta subseção mostra o Estado da Arte do tema proposto, onde é feito um resumo de artigos publicados em renomadas revistas na área de computação sobre o Snort e a paralelização de algoritmos de comparação de *strings*. A Seção 3 explica a Metodologia adotada para atingir os objetivos propostos. A Seção 4 traz a descrição completa dos algoritmos desenvolvidos, os resultados iniciais dos algoritmos Naive e Aho-Corasick executados na placa GT210 e a nova técnica de compactação. A Seção 5 tem foco na melhoria do algoritmo Aho-Corasick e expõe os resultados obtidos com as placas TESLA K20 e TITANX, além da CPU. Por último, é feita a conclusão do trabalho na Seção 6.

# 2. Snort, GPUs e Algoritmos de Comparação de Strings

As seções seguintes têm por finalidade apresentar conceitos sobre o Snort, as GPUs, os algoritmos de comparação de *strings* Força-bruta e o Aho-Corasick e mostrar o Estado da Arte sobre a paralelização de algoritmos de comparação de *Strings*.

# **2.1.** Snort

Uma ferramenta IDS serve basicamente para trazer informações sobre a rede, como: a quantidade de tentativas de ataques por dia, qual tipo de ataque foi usado, qual a origem dos ataques. A partir delas vai se tomar conhecimento do que se passa na rede e, em casos extremos, podem ser tomadas medidas cabíveis para tentar solucionar qualquer problema.

Nessas ferramentas existem dois tipos de limitações: 1) limitações de CPU que surgem devido à comparação de *strings* e 2) as limitações de Entrada e Saída causadas pelo *overhead* de leitura de pacotes na interface de rede (Jacob e Brodley, 2006). Para resolver o primeiro problema e amenizar o segundo, as pesquisas atuais vêm tentando fazer melhorias nos motores de comparação de *string* dos IDSs.

O Snort é um IDS que possui tecnologia de código aberto (Santos, 2005) para a detecção e prevenção de intrusão. Este IDS utiliza uma linguagem dirigida por regras, que combina os benefícios da assinatura de protocolo e os métodos de inspeção baseados em anomalia. Podemos ver na Figura 2.1 uma das várias regras que temos disponíveis no site do Snort. Basicamente a regra faz um alerta quando o protocolo tcp é usado e algum pacote é enviado de um dispositivo da rede externa por qualquer porta para algum dispositivo da rede interna pela porta 7597. Além disso, o alerta só será lançado se todas as regras que estão entre parêntesis forem atendidas. Por exemplo, o pacote enviado deve possuir a *string* "qazwsx.hsq" como indica a palavra-chave *content*.

```

alert tcp $EXTERNAL_NET any -> $HOME_NET 7597 (msg:"MALWARE-BACKDOOR QAZ Worm Client Login access";

flow:to_server,established; content:"qazwsx.hsq"; metadata:ruleset community; reference:mcafee,98775;

classtype:misc-activity; sid:108; rev:11;)

```

Figura 2.1: Exemplo de regra disponível no site do Snort.

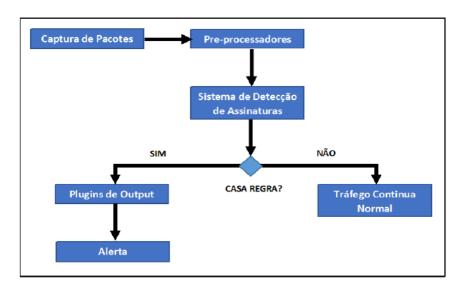

Com o intuito de ajudar na paralelização deste IDS, (Junta e Pereira, 2015) separaram e analisaram os componentes do Snort, os quais foram classificados em Mecanismo de captura, pré-processadores, mecanismo de detecção e plug-ins de saída, como pode ser visto no fluxograma de funcionamento do Snort da Figura 2.2.

Figura 2.2: Fluxograma de execução do Snort (Junta e Pereira, 2015).

O mecanismo de captura é a parte que monitora, em modo promíscuo, todo o tráfego do segmento onde ele está inserido, através das bibliotecas de captura de pacotes WinPcap no Windows e LibPcap no Linux. Os pré-processadores definem o tipo do pacote e como ele será tratado, através da ativação de *plugins* específicos para cada tipo de pacote, por exemplo: um pacote Telnet é tratado diferentemente de um pacote RPC neste componente. O Mecanismo de Detecção é o principal componente e onde ocorre a comparação de *strings*. Já os *Plugins* de Saída ficam responsáveis em decidir o que fazer caso a *string* seja encontrada.

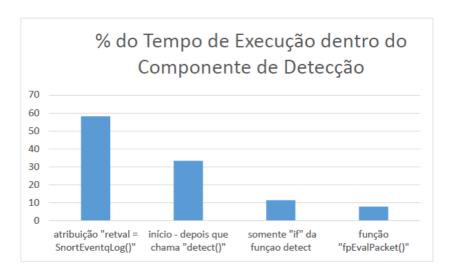

Inicialmente eles verificaram que o componente que mais consome CPU é o mecanismo de detecção com 76% do tempo de execução do Snort. Sendo assim, eles dividiram este componente de forma não aleatória em trechos de códigos e realizaram a medição do tempo de execução de cada trecho. Após obter os resultados, os trechos que tiveram tempos mais relevantes foram divididos novamente, realizando um aprofundamento no trecho. Assim por diante até que se obtivesse um trecho relativamente pequeno e que demandasse um tempo de execução relativamente grande. Deste modo, sugeriram começar a paralelização pelo trecho menor e com tempo de execução relevante, e posteriormente estender a paralelização para o trecho maior que contém o trecho já paralelizado. O resultado dessa metodologia adotada por eles pode ser visto no gráfico da Figura 2.3.

Figura 2.3: Percentual do tempo de execução dos trechos do componente de detecção (Junta e Pereira, 2015).

Com isso, eles sugerem que se inicie uma paralelização pela função "fpEvalPacket()", que está contida dentro da função "Detect()" e que demanda aproximadamente 77% do tempo de execução de "Detect()" e 7% do tempo de execução do componente de detecção. Após isso, paralelizar "Detect()" que está contido dentro do trecho "inicio do componente até depois que chama Detect()" e que demanda 33% da execução do trecho "inicio do componente até depois que chama Detect()" e 11% do tempo de execução do componente detecção. Para depois paralelizar este último trecho todo que demanda aproximadamente 33% do tempo de execução do componente de detecção.

# 2.2. Unidade de Processamento Gráfico (GPU)

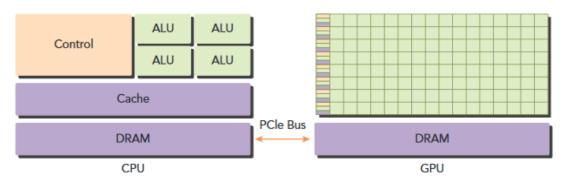

As Unidades de Processamento Gráfico (GPUs) são dispositivos processadores de elementos gráficos introduzidos na década de 1980 para descarregar os processamentos gráficos relacionados às Unidades Centrais de Processamento (CPUs) (KOUZINOPOULOS e MARGARITIS, 2008). As GPUs modernas são programáveis e possuem processadores de *streams* capazes de fazerem computação de alto desempenho, a qual tem evoluído consideravelmente depois do surgimento da arquitetura heterogênea CPU-GPU.

A computação heterogênea utiliza um conjunto de processadores com arquiteturas diferentes para executar uma aplicação (CHENG, et al., 2014). A Figura 2.4 ilustra esse cenário.

Figura 2.4: Ilustração de uma arquitetura heterogênea com CPU e GPU (CHENG, et al., 2014).

A CPU, também chamada de *core*, é a componente chave na computação de alto desempenho. Se há tempos atrás se colocava apenas um *core* em um chip de processamento formando as CPUs tradicionais, nos dias atuais tem-se colocados vários *cores* em um único chip, formando-se as CPUs *multicore* e as GPUs.

Diferentemente da arquitetura serial, que é classificada como Single Instruction Single Data (SISD), a GPU utiliza uma arquitetura Single Instruction Multiple Data (SIMD), onde uma única instrução é replicada e executada em vários *cores* da GPU de forma simultânea, e cada *core* opera sobre uma *stream* de dado diferente. Tenta-se com isso diminuir a latência (tempo necessário para uma operação começar e terminar – normalmente dada em milissegundos), e aumentar a largura de banda (quantidade de dados que pode ser processada por unidade de tempo – normalmente dada em bytes por segundo) e vazão (quantidade de operações que pode ser processada por unidade de tempo – normalmente dada em operações de ponto flutuante por segundo).

No trabalho com computação paralela, deve-se conhecer de forma sólida tanto os aspectos do hardware do dispositivo (arquitetura) como também seus aspectos de software (programação paralela).

A NVIDIA fornece algumas famílias de produtos, como a Tegra que foi projetada para dispositivos móveis e embarcados, Geforce para consumidor gráfico comum, Quadro para visualização profissional, e Tesla para computação paralela em Datacenter. Oferece a Fermi, o acelerador de GPU na família de produtos Tesla, que mostrou ser capaz de acelerar aplicações em muitas áreas como processamento sísmico, simulações de bioquímica, modelagem climática, processamento de sinais, entre outras. Após a Fermi lançou a Kepler que possui um poder de processamento muito maior que as gerações anteriores (CHENG, et al., 2014). Mais recentemente a Nvidia lançou as arquiteturas Maxuell e Pascal possuindo ainda mais poder de processamento.

|                   | FERMI<br>(TESLA C2050) | KEPLER<br>(TESLA K10) |

|-------------------|------------------------|-----------------------|

| CUDA Cores        | 448                    | 2 x 1536              |

| Memory            | 6 GB                   | 8 GB                  |

| Peak Performance* | 1.03 Tflops            | 4.58 Tflops           |

| Memory Bandwidth  | 144 GB/s               | 320 GB/s              |

Figura 2.5: Comparação entra as arquiteturas Fermi e Kepler (CHENG, et al., 2014).

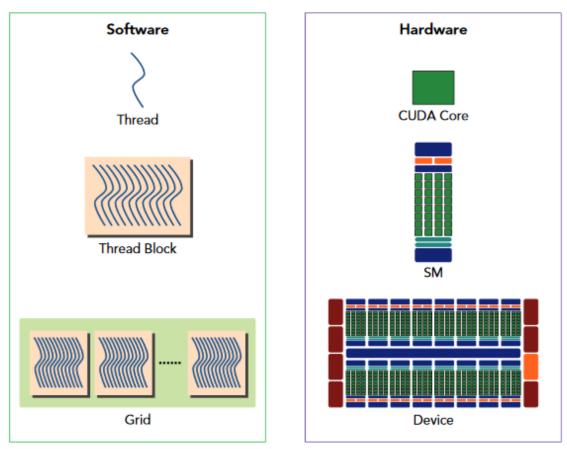

Para dar suporte à execução de uma aplicação CPU-GPU, a Nvidia projetou CUDA, um modelo de programação para computação heterogênea que permite acessar tanto a GPU como a CPU através de linguagem de programação. Seu compilador, no caso do CUDA C, o nvcc, é quem vai dividir o código que executará no host (CPU) e o que executará no device (GPU).

A arquitetura da GPU é construída em torno de uma matriz escalável de Multiprocessadores de Streams (SM). Alguns componentes que fazem parte desta arquitetura são:

- > CUDA Cores;

- Memória Compartilhada/ Cache L1;

- > Registradores;

- Unidades de Carga/Armazenamento;

- Unidades de Função Especial;

- > Agendador de Warp.

Cada SM em uma GPU é projetada para dar suporte à execução concorrente de milhares de *threads*. Quando um grid é lançado, os blocos de *threads* daquele grid são distribuídos entre os SMs disponíveis para execução. Após serem agendados em um SM, os *threads* de um bloco executam simultaneamente apenas na SM atribuída. Múltiplos grupos de *threads* podem ser atribuídos ao mesmo SM de uma vez e são agendados com base na disponibilidade de recursos SM. As instruções dentro de um único *thread* utilizam pipeline para alavancar o paralelismo no nível de instrução, somando-se ao já conhecido paralelismo em nível de dados (CHENG, et al., 2014).

CUDA utiliza uma arquitetura para gerenciar e executar *threads* em grupos de 32 chamados *warps*. Todos os *threads* em um mesmo *warp* executam a mesma instrução ao mesmo tempo, ou seja, em uma estrutura condicional, se a *thread* 1 estiver no *if* e todas as outras 31 *threads* já estiverem no *else*, as 31 *threads* esperarão o fim da execução do *if* da *thread* 1 para que todas as 32 *threads* executem o *else*. Isso significa que quanto mais existirem estruturas que mudem o fluxo normal do programa, a tendência é deixar o algoritmo menos eficiente.

Um bloco de *thread* é agendado em apenas um SM. Uma vez que ocorre o agendamento, ele permanece até a execução se completar. A Figura 2.6 mostra a correspondência dos componentes na visão lógica e na visão de hardware da programação em CUDA.

Figura 2.6: Visão lógica x visão de hardware da programação em CUDA.

A Figura 2.6 mostra que a programação de uma *thread* significa o uso de um determinado *core* da GPU. O bloco de *threads* significa o conjunto de *cores* de um dos SMs disponíveis. E o grid corresponde ao próprio SM.

Já a Figura 2.7 dá uma visão detalhada da arquitetura de uma GPU (aspecto físico), voltada para a hierarquia de memórias da mesma.

Figura 2.7: Arquitetura geral de uma GPU (Tran, et al., 2012).

- A memória global é uma área no off-chip DRAM gráfico DDR (G-DRAM ou comumente chamado como a memória do dispositivo). Através da memória global a GPU pode se comunicar com a CPU do host. Todos os dados do aplicativo residem inicialmente na DRAM e os pedidos a essa memória normalmente são atendidos usando transações de memória de 128 bytes ou 32 bytes, ou seja, a GPU lerá pacotes de 128 ou 32 bytes por vez.

- A memória compartilhada usa o mesmo epaço de 64 KB da cache L1, porém pode ser programada. Reside dentro de cada bloco de *thread* e é compartilhada entre os *threads* em execução por múltiplos processadores de *thread*. O tempo de acesso a essa memória é mais rápido se comparado com o da memória global.

- Os registradores são as memórias mais rápidas da GPU e são usados para armazenar temporariamente os dados usados nos cálculos da GPU em cada processador de *thread*, similar aos registradores da CPU. Este é um recurso escasso, tendo um limite de hardware de 63 registradores por *threads* na arquitetura Fermi e 255 na Kepler, por exemplo. É importante observar que arrays que não podem ter o índice determinado em tempo de compilação ou que são muito grandes para os registradores são colocados na memória local (uma memória residente no mesmo espaço da memória global).

- Cada thread tem sua própria memória local para carregar e armazenar os dados

necessários para os cálculos. A memória local é também uma área na G-DRAM. Assim, é também uma memória lenta.

- Além das memórias mencionadas anteriormente, há a memória constante e a memória de textura no G-DRAM. Os dados na memória constante e memória de textura podem ser armazenados em cache como dados somente leitura no chip do cache constante e do cache de textura, respectivamente. Vale ressaltar que a memória de textura é otimizada para localização espacial 2D, assim os threads que usam a memória de textura para acessar dados 2D alcançarão um melhor desempenho.

- Além das caches de textura e local, podem existir outras memórias caches não programáveis que ajudam no aumento do desempenho de memórias como a global e compartilhada.

Existem padrões de acessos a essas memórias que podem influênciar no desempenho da aplicação. O padrão de acesso alinhado ocorre quando o primeiro endereço de uma transação de memória do dispositivo é um múltiplo da granularidade da cache usada para atender a transação (32 bytes para cache L2 ou 128 bytes para cache L1). A realização de uma carga desalinhada causará perda de largura de banda. Já o padrão de acesso *coalesced* ocorre quando todos os 32 *threads* em um warp acessam um pedaço contíguo de memória.

O poder computacional da GPU é maior que o da CPU. Seu paralelismo em nível de dados além de um modelo de memória simplificado oferecidos por esses dispositivos tem atraído muitos pesquisadores para resolver problemas de desempenho em algoritmos convencionais (ou seja, não gráficos) que possuem desempenho mais baixo por causa da sua execução sequencial. Porém, existem desafios a se enfrentar quando uma aplicação convencional é transferida para a GPU. Em particular, o modelo de memória é restritivo quando se trata de implementar estruturas de dados bem conhecidas, tais como listas ligadas e árvores (Jacob e Brodley, 2006).

# 2.3. Algoritmos de Comparação de Strings

Os algoritmos podem ser classificados em uma faixa que vai desde facilmente paralelizáveis até completamente não paralelizáveis (ou programas inerentemente seriais). Essa classificação se aproximará de facilmente paralelizável a depender de alguns fatores, como a facilidade de dividir o problema em partes e a indepêndencia entre os resultados de cada parte. Já os algoritmos inerentemente seriais exigem os resultados de um passo anterior para realizer de forma eficaz a próxima etapa.

A multiplicação de matrizes é um bom exemplo de algoritmo facilmente paralelizável

uma vez que é possível calcular separadamente cada posição da matriz resultante e o resultado de uma posição não interfere no resultado das outras. No caso da comparação de *strings*, nosso objeto de estudo, existem vários algoritmos e devemos analisar a particularidade de cada um deles.

## 2.3.1. Naive (Força-Bruta)

O método Naive, mais conhecido como Força-Bruta, alinha a extremidade esquerda do padrão P com a extremidade esquerda do texto T e então compara os caracteres de P e T da esquerda para a direita até que qualquer um dos dois caracteres comparáveis sejam diferentes ou até P se esgotar, caso em que uma ocorrência de P é relatada. No outro caso, P é deslocado uma posição para a direita, e as comparações são reiniciadas a partir da extremidade esquerda de P. Esse processo é repetido até a extremidade direita de P passar sobre a extremidade direita de T (DAN, 1997).

No pior caso, o número de comparações feitas por esse método é  $\Theta(nm)$ , onde n é o tamanho de P e m o tamanho de T. Esse número de comparações pode se tornar inviável à medida que os tamanhos de P e T forem aumentando (DAN, 1997).

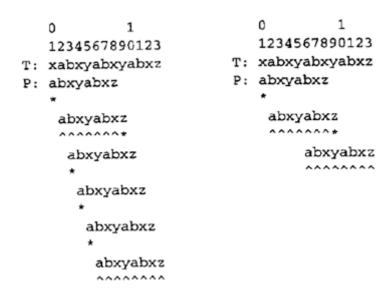

Existem técnicas para melhorar o método Naive, fazendo-o passar de  $\Theta(nm)$  para  $\Theta(n+m)$  no pior caso. Uma dessas ideias é tentar deslocar o padrão P em mais de uma posição quando não há a correspondência dos caracteres de P e T. A Figura 2.8 mostra essas ideias, usando P = abxyabxz e T = xabxyabxyabxz. Nesta figura, o asterisco indica que não houve correspondência, enquanto que o circunflexo indica que houve.

No primeiro cenário da Figura 3 (cenário à esquerda), onde é ilustrada a comparação do Naive puro, o algoritmo imediatamente encontra uma diferença entre P e T, devido à primeira comparação dos caracteres deles, e desloca P em uma posição. Os próximos 7 caracteres correspondem e as comparações são bem-sucedidas. Porém na nona comparação não há correspondência, sendo P deslocado uma posição e as comparações reiniciadas a partir da extremidade esquerda de P. Apenas a partir da sexta posição de T será detectada uma ocorrência de P. Para este exemplo são necessárias 20 comparações através do Naive Puro.

Figura 2.8: Ilustração do Naive Puro (à esquerda) e do Naive Melhorado (à direita) (DAN, 1997).

Um algoritmo mais inteligente pode perceber, depois da nona comparação, que as próximas três comparações não corresponderão. Este algoritmo, representado no segundo cenário da Figura 2.8 (cenário à direita), salta as três próximas comparações, e imediatamente move a extremidade esquerda de P para alinhar com a posição 6 de T. Para fazer isso, este algoritmo (chamado de Naive Melhorado) sabe que o primeiro caractere de P (especificamente 'a') não ocorre novamente em P até a posição 5 de P. Com isso ele conclui que o caractere 'a' não ocorre mais uma vez em T até a posição 6 de T, pois os três caracteres corresponderam e eram diferentes de 'a'.

#### 2.3.2. Aho-Corasick

O Snort v2.9.7.3 usa o algoritmo de Aho-Corasick (AC) para comparar o conteúdo dos pacotes que chegam na interface de rede com o conjunto de assinaturas de ataques configurado. Esse algoritmo de comparação de *string* tradicional é capaz de comparar múltiplos padrões simultaneamente percorrendo uma máquina de estado especial chamada máquina de Aho-Corasick, que difere de uma DFA (*Deterministic Finite Automaton*) comum, pois introduz uma nova transição definida como transição de falha para reduzir as transições de saída de cada estado (LIN, 2013).

O algoritmo AC invoca três funções (TRAN, et al., 2012): a função *goto* (g), a função de *falha* (f) e a função de *saída*. Para construir a função *goto*, (AHO e CORASICK, 1975) criam o *grafo goto*, iniciando apenas com um vértice que representa o estado 0. Após isso, o padrão "y" é adicionado através de novos vértices e novas arestas de modo que haverá, iniciando do estado inicial, um caminho para este padrão no grafo. Neste ponto a função de saída começa a ser construída e armazena o padrão na posição correspondente ao último

estado adicionado.

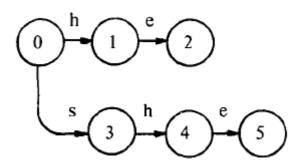

A inclusão de novos vértices e arestas no grafo *goto* nem sempre é necessária. Pode-se ver na Figura 2.9 que a inserção do padrão *his*, por exemplo, não necessita de uma aresta com o rótulo *h* saindo do estado 0, uma vez que esse rótulo já existe no grafo. Sendo assim, apenas os rótulos com os caracteres *i* e *s* deverão ser adicionados partindo do estado 1.

Figura 2.9: Construção do grafo goto (AHO e CORASICK, 1975).

Para finalizar a construção da função *goto*, eles adicionam um *loop* do estado zero para o próprio estado zero para todos os símbolos de entrada que não são capazes de realizar uma transição<sup>1</sup> do estado zero para outro estado.

(AHO e CORASICK, 1975) afirmam que a função *goto* pode ser armazenada das seguintes formas: em um vetor bidimensional (tabela), onde o acesso é em tempo constante, mas exige mais espaço de armazenamento, ou em uma lista linear, que necessita de menos espaço de armazenamento, porém, o tempo de acesso para g(s,a) é proporcional ao número de valores que não levam a máquina a uma falha no estado s (onde s é o estado atual e a o caractere de entrada). Eles também sugerem uma solução mista, onde os estados mais frequentemente usados, tal como o estado s0, sejam armazenados na tabela e os menos usados na lista linear.

A função de falha é construída a partir da função *goto*. A variável *depth* é definida como a menor distância de um estado *s* até o estado inicial. Primeiro calcula-se a função de falha para todos os estados de *depth* igual a 1, depois para os estados de *depth* igual a 2, e assim por diante. Para calcular a função de falha dos estados de *depth* igual a *d*, considera-se cada estado r de *depth* igual a d - 1, e faz as seguintes ações:

- 1. Se g(r,a) = falha para todo a, não faz nada.

- 2. Caso contrário, para cada símbolo a tal que g(r,a) = s, faz o seguinte:

- a. Faz state = f(r).

b. Executa a instrução  $state \leftarrow f(state)$  zero ou mais vezes, até a ser obtido para state tal que  $g(state, a) \neq falha$  (sendo que  $g(0,a) \neq falha$  para todo a).

<sup>&</sup>lt;sup>1</sup> Uma transição indica uma mudança de estado e é descrita por uma condição que precisa ser realizada para que a transição ocorra.

c.  $\overline{\text{Faz } f(s) = g(state, a)}$ .

A função de saída também é atualizada durante a construção da função de falha. Ao determinar que f(s) = s, faz-se a união das saídas do estado s com as saídas do estado s.

Como exemplo, a Figura 2.10 mostra as funções utilizadas pela máquina AC para o conjunto de padrões {"he", "she", "his", "hers"}:

- O grafo orientado da Figura 2.10 (a) representa a função *goto* (onde ¬ ('h', 's') denota todos os outros símbolos de entrada diferentes de 'h' e 's'). A função *goto* mapeia um par consistindo de um estado e um símbolo de entrada dentro de um estado ou uma mensagem de falha. Por exemplo, a borda marcada como h do estado 0 para o estado 1 indica que o *g* (0, 'h') = 1. A ausência de uma seta indica falha.

- A função de falha mapeia um estado para outro estado. Ela é consultada sempre que a função goto relata uma falha.

- A função de saída mapeia um conjunto de palavras-chaves para a saída com os estados designados.

Figura 2.10: Funções usadas no algoritmo AC (Tran, et al., 2012).

Agora assuma o texto "ushers". A máquina AC trabalha da seguinte maneira: iniciando no estado 0, a máquina volta pro estado 0 uma vez que g(0, 'u')=0. Pela mesma razão, a máquina entra nos estados 3,4,5 sequencialmente enquanto processa as strings 's', 'h', 'e' (g(0, 's')=3, g(3, 'h')=4, g(4, 'e')=5) e emite a saída, indicando que ele encontrou as palavras "she" e "he". Depois a máquina avança para o próximo símbolo de entrada 'r'. Uma vez que g(5, 'r')=falha, a máquina entra no estado 2=f(5) (Figura 2.10b). Então, uma

vez que g(2, r')=8, g(8, s')=9 a máquina AC entra no estado 9 e emite a saída "hers".

## 2.4. Estado da Arte

# 2.4.1. Algoritmo Paralelo PFAC

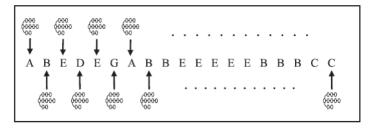

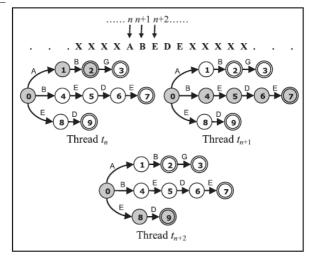

LIN, C. et al. (2013) propuseram uma máquina de estado que executa um algoritmo paralelo bastante eficiente chamado de *Parallel Failureless Aho-Corasick* (PFAC). Essa máquina é semelhante à máquina de Aho-Corasick, mas não utiliza as transições de falha existentes na mesma. Somado a isso, foram introduzidas as seguintes técnicas que otimizam as execuções da GPU: redução de transações do *buffer* de entrada da memória global, redução da latência de consulta à tabela de transição, eliminação da tabela de acessos de saída, evitando conflito de banco da memória compartilhada, e o melhoramento da transmissão de dados via PCI Express.

O PFAC aloca uma *thread* para cada caractere de uma *stream* de entrada a fim de identificar qualquer padrão começando na posição inicial da *thread*, O número de *threads* alocadas é igual ao tamanho da *stream*. Nesse algoritmo, se o caractere em análise não levar a máquina para outro estado, a *thread* imediatamente termina sua tarefa. Por exemplo: se a primeira letra da *stream* de entrada conseguir levar a máquina para outro estado, a segunda letra é analisada pela *thread*; se a segunda não for encontrada na máquina de estado toda a *string* é descartada.

As Figuras 2.11 e 2.12 exemplificam bem essa situação. Na Figura 2.11 é possível ver algumas *threads* com uma máquina de estado para cada caractere de entrada. A primeira *thread* chegará ao estado 2 (um dos estados finais da máquina) devido às entradas 'A' e 'B', mas, diferentemente do Aho-Corasick original, não irá para um estado de falha quando o caractere 'E' for analisado pela máquina. Já a segunda *thread* fará sua comparação de *string* a partir do caractere 'B', como pode ser visualizado nas Figuras 2.11 e 2.12.

Figura 2.11: Algoritmo PFAC (LIN et al., 2013).

Resumidamente, notamos pela Figura 2.12 que em vez de usar uma *thread* para encontrar três padrões, ele usa três threads para encontrar três padrões em paralelo.

Figura 2.12: Exemplo do PFAC para os padrões "AB", "ABG", "BEDE", e "ED" (LIN et al., 2013).

Para realizar os experimentos, os autores compararam o desempenho do algoritmo Aho-Corasick no Intel Core i7-950 e o algoritmo PFAC na NVIDIA GTX580 (além de fazerem uma versão do PFAC para a CPU com o OpenMP chamada *PFAC<sub>OMP</sub>*). Mais especificamente, eles tem um *host* com uma CPU Intel Core i7-950 executando o sistema operacional Linux, com memória DDR3 de 12GB em uma placa mãe ASUS P6T-SE, e um dispositivo equipado com uma GPU GTX580 GeForce da NVIDIA no mesmo sistema Core i7 com driver NVIDIA versão 260.19.29 e o CUDA versão 3.2.

Os padrões de teste foram retirados do Snort V2.8 e as *streams* de entrada foram extraídas de pacotes DEFCON que contém grandes quantidades de padrões de ataques reais e são amplamente utilizadas para testes de NIDS (*Network Intrusion Detection Systems*) comerciais.

As métricas utilizadas na comparação foram as seguintes (LIN et al., 2013):

- 1) Taxa de transferência de dados bruta:  $\frac{8n}{T_{GPU}}$ , onde 8n é o total de bits de uma stream de entrada de n caracteres e  $T_{GPU}$  o tempo de execução do kernel no núcleo da GPU.

- 2) Largura de banda efetiva do PCIe:

$\frac{8n}{T_{host/dispositivo}}$ , onde 8n é o total de bits de entrada (sendo n é o número de caracteres de entrada) e  $T_{host/dispositivo}$  o tempo para mover o dado do host para o dispositivo via PCIe;

e  $\frac{16n}{T_{\text{dispositivo/host}}}$ , onde 16n é o total de bits do resultado da comparação dos padrões

e  $T_{dispositivo/host}$  o tempo para mover os resultados da comparação do dispositivo para o host via PCIe.

3) Taxa de transferência do Sistema:  $\frac{8n}{T_{total}}$ , onde 8n é o total de bits de entrada e T é  $T_{GPU}$ ,  $T_{host/dispositivo}$  e  $T_{dispositivo/host}$ .

Após a execução dos testes, o desempenho do PFAC mostrou-se bastante superior ao do algoritmo Aho-Corasick. Para pacotes de entrada DEFCON de 256 MB, o PFAC<sub>GPU</sub> alcançou 143,16 Gbps de taxa de transferência de dados bruta, enquanto que o AC<sub>CPU</sub> e o PFAC<sub>OMP</sub> alcançaram 1,91 e 12,61 Gbps, respectivamente. Ou seja, os resultados experimentais mostraram que o algoritmo proposto executado na GPU NVIDIA é 74,95 vezes mais rápido do que o algoritmo Aho-Corasick implementado em uma CPU se for contabilizado apenas a taxa bruta. O autor enfatizou bem este resultado, porém também foi importante mostrar a taxa do sistema (ver Figura 2.13) que, ao levar em consideração as transferências entre CPU e GPU, deu uma reduzida na taxa de transferência da versão de GPU, mas que mesmo assim foi superior a todas as outras versões implementadas.

| DEFCON Packets |                             | AC <sub>CPU</sub>                | DPAC <sub>OMP</sub>              | PFAC <sub>OMP</sub>              |                                  | PFAC <sub>GPU</sub>                        |                                |  |  |

|----------------|-----------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|--------------------------------------------|--------------------------------|--|--|

| Input Size     | # of<br>matched<br>Patterns | Raw data<br>Throughput<br>(Gbps) | Raw data<br>Throughput<br>(Gbps) | Raw data<br>Throughput<br>(Gbps) | Raw data<br>Throughput<br>(Gbps) | H2D / D2H<br>Effective Bandwidth<br>(Gbps) | System<br>Throughput<br>(Gbps) |  |  |

| 32 MB          | 458,491                     | 1.55                             | 8.73                             | 9.51                             | 110.64                           | 47.92 / 51.20                              | 14.48                          |  |  |

| 64 MB          | 840,956                     | 1.58                             | 8.96                             | 9.89                             | 119.37                           | 48.00 / 51.28                              | 14.68                          |  |  |

| 128 MB         | 933,759                     | 1.82                             | 9.73                             | 11.79                            | 135.02                           | 48.08/ 51.28                               | 14.87                          |  |  |

| 256 MB         | 1,118,653                   | 1.91                             | 9.71                             | 12.61                            | 143.16                           | 48.08 / 51.28                              | 15.00                          |  |  |

Figura 2.13: Comparação das taxas de transferências com pacotes DEFCON de tamanhos diferentes (LIN et al., 2013).

Em outro experimento LIN, C. et al. (2013) compararam o PFAC executando em outras gerações de GPUs, como: GTX 580, GTX 480, GTX 295 e Tesla M2050. Foi verificado que o PFAC alcança um maior desempenho nas novas gerações de GPUs Nvidia com mais núcleos, largura de banda de memória e maior capacidade de computação.

O lado negativo da abordagem é que o PFAC pode ter problemas em relação ao desbalanceamento de cargas, pois as *threads* que ficam responsáveis pelas maiores cargas dominam o tempo de execução de uma *warp*.

#### 2.4.2. Memórias Compartilhadas e Caches de Textura da GPU

Em outro trabalho, TRAN, N. et al. (2012) apresentaram uma nova técnica de paralelização a qual armazena de forma eficiente os dados do texto de entrada e os dados de referência (padrões de comparação) nas memórias compartilhadas e caches de texturas da GPU. Além disso, a nova abordagem programou eficientemente os acessos à memória a fim de minimizar a sobrecarga de dados nas memórias compartilhadas.

Para o uso eficiente da memória, eles colocaram cuidadosamente os dados de entrada e

os dados de referência. Para os dados de entrada, cujo tamanho é de pelo menos algumas centenas de megabytes, eles podem ser total ou parcialmente colocados na memória global do DRAM-Gráfico (GDRAM), também conhecida como memória do dispositivo. No entanto, eles são grandes demais para caber nas memórias compartilhadas e caches de textura. Por conseguinte, a fim de carregar os dados de entrada de forma eficiente para a memória compartilhada, os autores organizaram cuidadosamente os pedidos de acesso à memória, de modo que o número de acessos à memória global pôde ser minimizado.

Eles organizaram os dados de referência, com o qual os dados do texto de entrada são comparados, em uma tabela bidimensional chamada Tabela de Transição de Estado (STT) e colocaram esses dados na memória de textura de modo que a parte usada ativamente da STT pôde ser armazenada na cache de textura. A abordagem reduziu significativamente as latências médias de acesso à memória para carregar ambos os dados de entrada e os dados de referência, e levou a melhorias de desempenho para o algoritmo AC.

A Figura 2.14 mostra um exemplo da STT, onde as linhas representam os estados e as colunas representam os caracteres de entrada. Ela é uma tabela comum que é acessada por todas as *threads* aleatoriamente para a comparação de padrão.

|        | Matching? |   |   | Input symbols |   |   |     |     |   |     |

|--------|-----------|---|---|---------------|---|---|-----|-----|---|-----|

|        |           | _ | _ |               |   |   |     |     |   |     |

|        |           | М | 0 | 1             | 2 |   | 100 | 101 |   | 255 |

|        | 0         | 0 | 0 | 0             | 1 | 0 | 0   | 0   | 0 | 0   |

|        | 1         | 0 | 0 | 0             | 0 | 5 | 0   | 0   | 0 | 0   |

|        | 2         | 0 | 0 | 0             | 0 | 0 | 0   | 0   | 0 | 0   |

|        | 3         | 0 | 0 | 0             | 0 | 0 | 0   | 0   | 0 | 0   |

| se     | 4         | 0 | 0 | 0             | 8 | 0 | 0   | 0   | 0 | 0   |

| States | 5         | 1 | 0 | 0             | 0 | 0 | 0   | 0   | 0 | 0   |

|        | 6         | 0 | 0 | 0             | 0 | 0 | 0   | 0   | 0 | 0   |

|        | 7         | 0 | 0 | 0             | 0 | 0 | 0   | 9   | 0 | 0   |

|        | 8         | 0 | 0 | 0             | 0 | 0 | 0   | 9   | 0 | 0   |

|        | 9         | 1 | 0 | 0             | 0 | 0 | 0   | 0   | 0 | 0   |

|        |           |   |   |               |   |   |     |     |   |     |

Figura 2.14: Ilustração da Tabela de Transição de Estado (TRAN et al., 2012).

Eles trabalharam com duas novas abordagens:

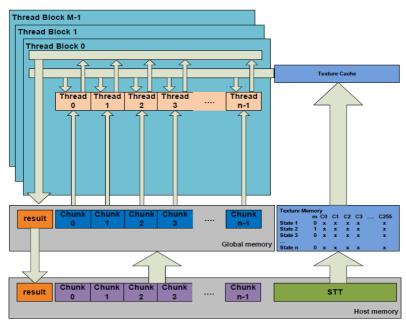

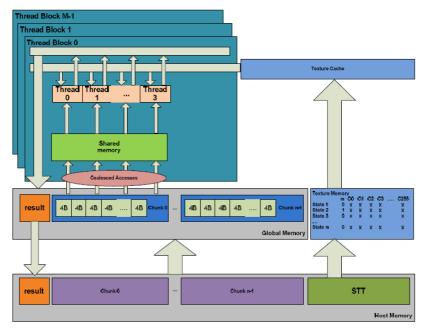

1) **Usando memória global (Figura 2.15):** Nesta abordagem o AC foi paralelizado de maneira direta, armazenando os dados do texto de entrada na memória global. Esses dados foram divididos em vários *chunks*. Cada *chunk* foi atribuído a cada processador de *thread* no mesmo bloco de *thread*. Ao final, cada *thread* aplica a comparação de padrão no seu próprio *chunk*.

Figura 2.15: Ilustração da abordagem de memória global (TRAN et al., 2012).

2) Abordagem de memória compartilhada (Figura 2.16): Nesta abordagem os dados também foram divididos em *chunks*, mas foram levados da memória global para a memória compartilhada usando uma leitura coordenada chamada Acesso *Coalesced* (TRAN et al., 2012).

Figura 2.16: Ilustração da abordagem de memória compartilhada (TRAN et al., 2012).

Para a execução do experimento, usaram CUDA na GPU NVIDIA GeForce 9500 GT, uma placa mais antiga se comparada com a placa GTX580 utilizada nos experimentos do PFAC da subseção 2.4.1. Ela é uma placa de baixo desempenho, contem apenas 32 processadores de *streams* (ou processadores de *threads*) organizados em 4 multiprocessadores (ou blocos de *threads*), operando a 1,35 GHz com 256 MB de memória do dispositivo. Já o sistema experimental completo usou um processador multicore da Intel

(2,2 GHz Intel Core2Duo 4) com 2GB de memória principal. O SO usado foi o Linux 5.5 CentOS.

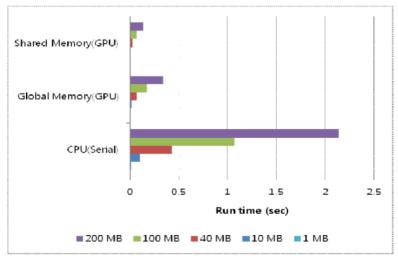

Os autores (TRAN, N. et al., 2012) realizaram três experimentos: Algoritmo AC na versão serial, na versão memória global e na versão memória compartilhada. Diferentes tamanhos de textos de entradas e quantidades diferentes de padrões foram usados para medir o desempenho.

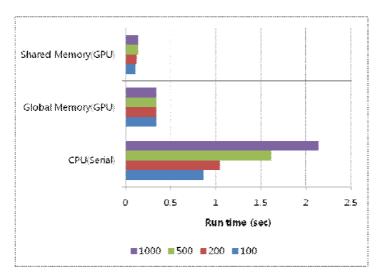

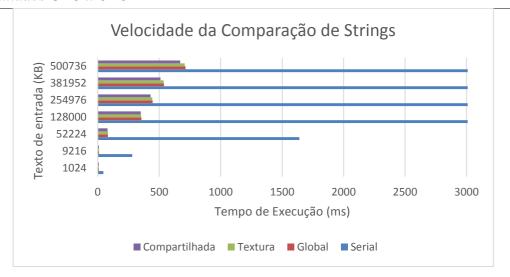

A Figura 2.17 mostra a comparação do tempo de execução das três abordagens usando diferentes tamanhos de *strings* de entrada e fixando o número de padrões em 1000.

Figura 2.17: Resultado das três abordagens usando 1000 padrões (TRAN et al., 2012).

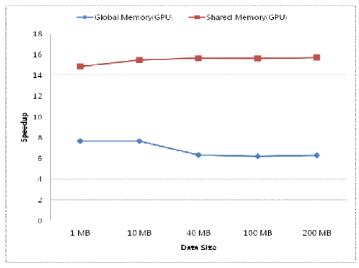

A Figura 2.18 mostra a comparação das velocidades da versão de memória global e da versão de memória compartilhada com a velocidade da memória serial. A velocidade máxima alcançada nessa comparação foi 15,72 vezes usando um texto de entrada de 200 MB e 1000 padrões na versão de memória compartilhada. Já na versão de memória global a velocidade foi de 4,71 a 5,76 vezes comparado com a versão serial.

Figura 2.18: Comparação das velocidades (TRAN et al., 2012).

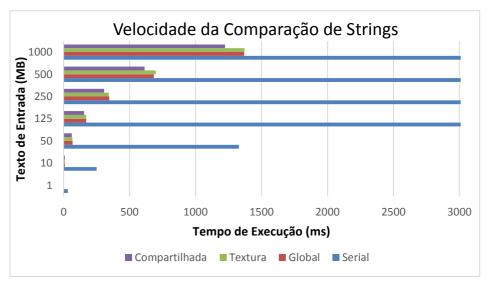

Já em um segundo experimento, o tamanho do texto de entrada foi fixado em 200 MB e o número de padrões foi sendo aumentado até 1000 padrões, como mostra a Figura 2.19.

Figura 2.19: Resultado das três abordagens para 200 MB de texto de entrada (TRAN et al., 2012).

Como pode ser visto na Figura 2.19, o tempo de execução das duas versões paralelas na GPU alteraram insignificantemente com o número de padrões. Isto foi especialmente verdadeiro para a versão de memória global.

#### 2.4.3. **GPU** x **CPU**

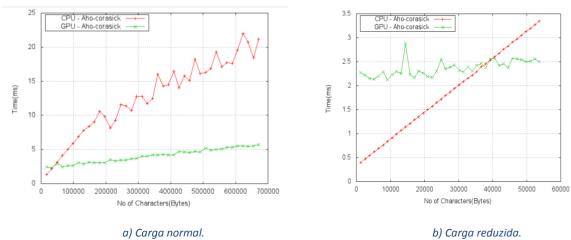

THAMBAWITA, D. et al. (2014) mostraram quando as GPUs podem ser usadas para aplicações de correspondência de *strings* usando o algoritmo de Aho-Corasick como referência. Para isso, eles compararam o desempenho do Aho-corasick em uma CPU e uma GPU a fim de identificar o dispositivo adequado para obter o melhor desempenho. Essa comparação foi feita tendo a mudança de tamanho dos dados de entrada como o principal parâmetro.

Para o experimento foi usada uma versão serial do algoritmo Aho-Corasick, chamada Multifast (que é o algoritmo geral do Aho-Corasick, com transições de falha e sem quaisquer técnicas de processamento paralelo) e na versão paralela foi usado o PFAC (implementado em CUDA), sendo que o multifast foi executado em uma CPU Intel Core i5-3230M @ 2.60GHz com 3 MB de cache e o PFAC em uma GPU NVIDIA GeForce GT 740M de 384 cores CUDA.

Mediu-se o tempo de execução do experimento em milisegundos, mas alguns fatores foram desconsiderados, como o tempo para inicializar a GPU e o tempo para execução da função *printf()*, porque esses fatores afetam diretamente o tempo medido. Portanto, ambos foram ignorados do tempo medido.

Eles usaram como padrões cinco permutações usando vinte e seis caracteres do alfabeto inglês (Exemplo: abcdefghijklmnopqrstuvwxyz). Também adicionaram o alfabeto inglês repetidamente dentro de um arquivo de texto para ser usado como arquivo de texto de

entrada para o experimento.

No primeiro experimento eles aumentaram o tamanho do arquivo de entrada de 16375 bytes para 671375 bytes e obtiveram o resultado mostrado na Figura 2.20a.

Figura 2.20: CPU e GPU com Aho-Corasick (Thambawita et al., 2014).

Um importante ponto de mudança pôde ser identificado sobre o gráfico da Figura 2.20a próximo a 40000 bytes (onde o desempenho da GPU ficou abaixo da CPU). Por isso, eles fizeram outro experimento mudando o tamanho do arquivo de 1310 a 53710 bytes e obtiveram o resultado mostrado na Figura 2.20b.

Pode-se notar que o ponto de mudança ocorreu por volta dos 40000 bytes (40 kB). Portanto, para fazer comparação de *string* com um algoritmo como o Aho-Corasick e um arquivo de entrada de tamanho menor que 40000 bytes é melhor usar a CPU do que a GPU.

## 2.4.4. Paralelização de vários Algoritmos

Por fim, o trabalho de Kouzinopoulos e Margaritis (2008) analisou as parelizações dos algoritmos de comparação de *strings* Naive, Kanuth-Morris-Pratt, Boyer-Moore-Horspool e o Quick-Search, feitas usando a plataforma CUDA. O conjunto de dados e a metodologia experimental tiveram 3 sequências de referências no contexto da bioinformática: 1) o genoma bacteriano da Yersinia pestis (4,6 Mb de tamanho); 2) do Bacillus anthracis (5,2 Mb de tamanho); 3) um Cromossomo Artificial Bacteriano (BAC) simulado do Homo Sapiens. O padrão de consulta foi construído de subsequências escolhidas aleatoriamente a partir de cada sequência de referência com um comprimento de 25, 50, 200 e 800 caracteres. A partir desse conjunto de dados, eles compararam cada algoritmo com sua respectiva versão serial e seu melhor resultado foi quando paralelizou o Boyer-Moore-Horspool obtendo uma velocidade 20 vezes maior em relação a sua versão serial e 24 vezes maior quando passou a usar memória compartilhada em relação à sua versão com memória

global.

## 2.4.5. Mapeamento Sistemático do Algoritmo AC paralelo

JÚNIOR, J. B. S. et al. (2016) fizeram um mapeamento sistemático acerca do algoritmo AC paralelo em revistas renomadas na área de computação. Eles conseguiram levantar 22 artigos que fizeram a paralelização em uma GPU e mostraram que máquina AC é colocada na memória de textura em 61,11% dos experimentos, inclusive nos trabalhos citados acima. Apenas LIN et al. (2010) usaram a memória compartilhada, porém, devido ao pouco espaço de armazenamento disponível nessa memória, eles não conseguiram executar a STT completa e tiveram que dividir a STT por grupos de ataques, lançando determinada STT à medida que a *string* chegue na GPU. Dessa forma, é necessário realizar uma préfiltragem na *string* que será comparada, para saber qual STT será lançada, e essa préfiltragem faz o algoritmo ficar mais lento.

Além disso, eles mostraram também as técnicas de otimização aplicadas nos trabalhos encontrados, como por exemplo, para aumentar o desempenho do algoritmo, TRAN et al. (2012, 2013) fizeram com que a parte mais usada da STT ficasse na cache de textura. Já VILLA et al. (2012) aproveitaram a própria STT para dizer se o próximo estado era um estado final ou não. Para isso, cada posição da STT tem 32 bits, sendo que os 31 primeiros indicam o próximo estado e o último indica um *flag* de estado final. Dessa forma retira-se a necessidade de construir outra tabela para informar se é um estado final (ou estado de aceitação). LIN et al. (2013) implementaram a STT na memória de textura e afirmam que como o estado inicial é o mais acessado, a primeira linha da STT (que representa o estado inicial) é colocada na memória compartilhada, já que o acesso a essa memória é mais rápido que à memória de textura.

Um ponto interessante a se observar é que nem sempre é possível colocar a STT completa na memória devido à limitação de espaço de armazenamento. LIN et al. (2010), que implementaram a STT na memória compartilhada, dividiram a STT por grupos de ataques. VILLA et al. (2012), implementaram na memória de textura, mas se a STT for muito grande ela é lançada por partes.

O espaço de armazenamento limitado também fez com que alguns autores compactassem a STT. Tanto PUNGILA (2013, 2015) como BELLEKENS (2014) fizeram uma compressão no DFA e usaram a técnica de bit-mapeamento para representá-lo. PUNGILA (2013) usou comparação de prefixos afirmando que um prefixo de profundidade igual a 8 é suficiente para produzir uma taxa de falso positivo de apenas 0,0001%. Já PUNGILA (2015) usou o algoritmo de compressão chamado Lempel-Ziv-

Welch para diminuir o tamanho do DFA e o bit-mapeamento para compactar a STT formada a partir do DFA reduzido.

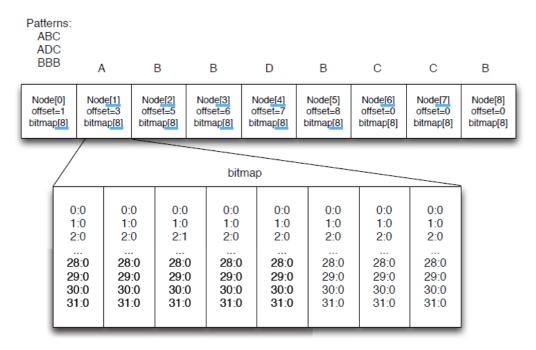

## 2.4.6. A técnica de compactação por Bit-mapeamento

Tanto PUNGILA (2013, 2015) e BELLEKENS (2014) usaram a técnica de bitmapeamento para representar o DFA. Nessa técnica, também conhecida como mapeamento por bit, cada nó do DFA tem um bitmap associado (um *array* de 8 células de 32 bits cada uma) onde seus filhos são representados nesse mapa de 256 bits, sendo que cada bit corresponde a uma letra do alfabeto ASCII (BELLEKENS, 2014). Cada bit no bitmap do nó setado como 1 representa uma transição válida para aquele nó. Com isso, os autores não necessitaram mais representar todas as combinações possíveis entre estados e caracteres de entrada, conforme é feito na STT comum.

A Figura 2.21 ilustra como os nós são organizados. O primeiro nó ('A') tem dois filhos, 'B' e 'D'. O *offset* do nó 1 apenas aponta para o seu primeiro filho (nó 3) correspondente a letra 'B', no entanto, para acessar o segundo nó ('D') é realizado um cálculo: faz-se a soma do número de bits setados como 1 no bitmap que sejam anteriores ao caractere de entrada pretendido. Neste caso, o bitmap tem 2 valores setados como 1, em 'A' (66 em decimal ASCII) na coluna 3/posição 2 e em 'D' (68 em decimal ASCII) que na Figura 2.21 está implícito na coluna3/posição 4, ou seja, o único setado como 1 antes de 'D' é 'B'. A transição é calculada da seguinte forma: nóAtual = *offset* + i, onde *offset* é o *offset* do primeiro nó e i é o valor da soma. Como i é igual a 1 e o offset de 'A' é igual a 3, o segundo filho pode ser encontrado na posição 3+1=4, que corresponde ao nó 4 da Figura 2.21.

Figura 2.21: Ilustração do bitmap correspondente ao primeiro nó de um DFA (BELLEKENS, 2014).

## 2.5. Considerações Finais do Capítulo

Este capítulo deu uma visão geral sobre o funcionamento do Snort, das GPUs e de como andam as pesquisas sobre a paralelização dos algoritmos de comparação de *strings* através de GPUs, com foco no algoritmo Aho-Corasick. Com isso, nota-se que as GPUs têm sido uma ferramenta eficaz na aceleração da comparação de *strings* e que elas têm uma importante hierarquia de memória que pode ser explorada a fim de aumentar ainda mais o desempenho da busca dos padrões nos pacotes de redes. Por fim, algumas técnicas de otimizações e compactações podem ser necessárias devido ao tamanho limitado de suas memórias.

# 3. Metodologia da Pesquisa

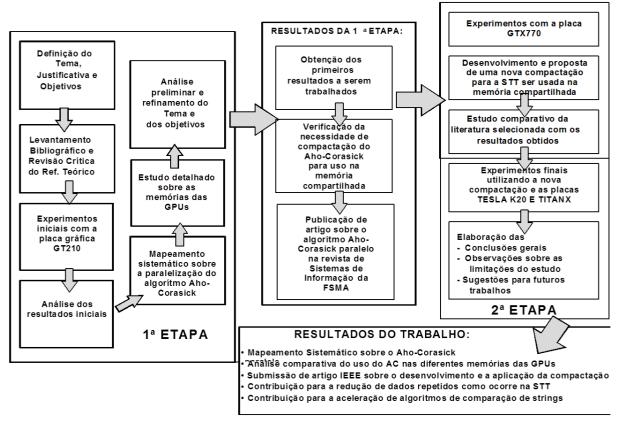

Com base nos pressupostos teóricos, alguns dos principais algoritmos de comparação de *strings* foram paralelizados, de modo que fosse possível avaliar diversos cenários, comparando os algoritmos paralelizados entre si e entre suas versões seriais, a fim de verificar aquele que obteve o melhor desempenho para implementá-lo no IDS Snort. Utilizou-se a plataforma de computação paralela CUDA da Nvidia como recurso necessário para a paralelização dos algoritmos.

Através do processo de pesquisa da Figura 3.1 foi possível estudar, analisar, discutir e identificar a melhor forma de buscar padrões em um texto de forma paralela.

Figura 3.1: Etapas da pesquisa.

#### 3.1. Materiais e Métodos

Para a implementação do proposto na Metodologia, foi necessária a utilização dos seguintes recursos:

- ➤ Hardware e Software do Sistema

- o Características da máquina de teste **GT210**:

Sistema Operacional Windows 8;

Processador Intel Pentium Dual Core E5700 de 3.0 GHz;

Memória RAM: 4 GB;

GPU: GEFORCE 210;

CUDA Cores: 16;

Clock da GPU: 589 MHz;

Memória Global: 1 GB;

Taxa de Transferência da memória (Bandwidth): 8 GB/s.

o Características da máquina de teste **Tesla K20**:

Sistema Operacional RedHat 6.4;

Processador Intel Xeon Ten-Core E5-2660v2 de 2.2 GHz;

Memória RAM: 64 GB;

GPU: NVIDIA TESLA K20;

CUDA Cores: 2496;

Clock da GPU: 706 MHz;

Memória Global: 5 GB.

Taxa de transferência da memória (Bandwidth): 208 GB/s

O Características da máquina de teste **Titanx**:

Sistema Operacional Linux 3.19.0-80-generic #88~14.04.1-Ubuntu;

Processador Intel Core i5 1,2 GHz 6ª geração;

Memória RAM: 8 GB;

GPU: NVIDIA TITAN X (Pascal);

CUDA Cores: 3584;

Clock da GPU: 1417 MHz;

Memória Global: 12 GB;

Taxa de transferência da memória (Bandwidth): 480 GB/s;

#### Características da máquina de teste CPU:

Sistema Operacional Windows 8.1 de 64 bits;

Processador Intel Core i3-4005U 1,70 GHz;

Memória RAM: 4 GB;

GPU: Não possui;

Neste trabalho, foi realizada a paralelização dos algortimos Naive (Força-Bruta) e Aho-Corasick, sendo que a análise de desempenho dos mesmos pode ser vista mais adiante nas seções 4 e 5.

Inicialmente foi necessário decidir em usar o algoritmo Naive em sua versão pura, ou seja, sem nenhuma técnica que acelere seu processamento, ou o Naive Melhorado. Após essa decisão, começaram os experimentos de comparação entre o Naive e o Aho-Corasick paralelos. O texto usado nesses experimentos iniciais para buscar os padrões pode ser visto no anexo C. Esse texto foi replicado dez vezes se tornando um texto de 40960 bytes. Já os padrões utilizados foram: {"Brazil", "it", "home", "primeiro", "today", "in", "and", "the"}.

Para usufruirmos da computação paralela possibilitada pela GPU, seguimos a abordagem de *chuncks*, dividindo o texto de entrada em fragmentos que são processados em paralelo, como TRAN, N. et al. (2012) fizeram em seu trabalho. Ainda baseado no trabalho deles, também exploramos a hierarquia de memórias disponível nas GPUs criando três abordagens diferentes para o Naive e três para o Aho-Corasick. Adicionalmente, exploramos a ocupância dos programas nos núcleos da GPU a fim de verificar o impacto que esta métrica pode proporcionar ao desempenho dos algoritmos paralelos.

Com a finalização dos experimentos iniciais na placa GT210, verificou-se que o algoritmo Naive teve um desempenho inferior ao algoritmo Aho-Corasick e, por isso, os experimentos finais voltaram-se para o aperfeiçoamento do Aho-Corasick paralelo. Passou-se a utilizar padrões de ataques reais, retirados de dezenove regras do Snort, além de pacotes de redes como texto de entrada. Neste ponto, notou-se que não seria possível executar a STT como uma matriz bidimensional na memória compartilhada das GPUs TITAN X e TESLA K20 devido à baixa capacidade de armazenamento dessa memória. Por conseguinte, foi necessário diminuir o tamanho da STT, sendo aplicada uma nova técnica de compactação, a qual pode ser vista em detalhes na Seção 3.4.

# 4. Paralelização Inicial e Compactação do Aho-Corasick

Nesta seção é descrita a implementação dos algoritmos desenvolvidos no trabalho, incluindo os detalhes sobre suas estruturas. De forma geral, os algoritmos Força-Bruta e Aho-Corasick foram paralelizados através da plataforma de computação paralela CUDA da Nvidia. Ao final, o Aho-Corasick paralelo foi compactado a fim de possibilitar sua execução na memória compartilhada com o intuito de se obter *speedups* cada vez maiores.

## 4.1. Comunicação CPU - GPU

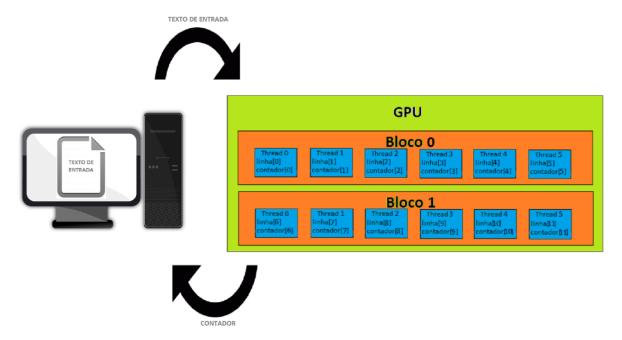

A Figura 4.1 ilustra como a CPU se comunica com a GPU e quais variáveis são enviadas de uma plataforma para outra. O texto de entrada, o qual possui os pacotes de redes onde os padrões de ataques são buscados, fica armazenado em um arquivo de texto no formato de uma matriz.

Figura 4.1: Ilustração do processamentos dos softwares.

O texto em matriz é enviado da CPU para a GPU através da função *main*. Cada *thread* da GPU processa uma linha da matriz e conta a quantidade de padrões encontrados. Ao final do processamento, o contador é enviado para o host.

A função *main* também é responsável pela chamada ao *kernel* de comparação de *strings* na GPU e pelo cálculo do tempo de execução médio desse *kernel* através do *event* do CUDA. Ao final, o tempo médio e a quantidade de padrões encontrados no texto são impressos na tela. A taxa de transferência, medida em Megacaracteres por segundo (Mcps),

é calculada através da quantidade de caracteres total do texto de entrada dividida pelo tempo de execução do algoritmo.

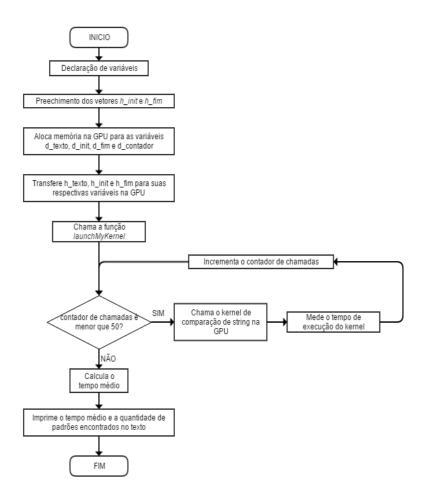

O fluxograma completo da função *main* nos testes iniciais pode ser visto na Figura 4.2.

Figura 4.2: Fluxograma da função main de todos os algoritmos desenvolvidos nos testes iniciais.

A função "launchMyKernel" é disponibilizada no site da Nvidia (Harrys). Ela foi implementada e adaptada com duas finalidades bem definidas:

1) Atribuir os valores do tamanho do grid e do bloco. Essa atribuição pode ocorrer diretamente atribuindo valores desejados às variáveis gridSize e blockSize ou ser calculada através da função cudaOccupancyMaxPotentialBlockSize, que calcula dinamicamente tamanhos de blocos que atinjam uma ocupância máxima teórica, e, após isso, calcula-se o tamanho do grid com a fórmula:

$$gridSize = (arrayCount + blockSize - 1)/blockSize.$$

Eq. 3.1

2) Medir a ocupância teórica com a função cudaOccupancyMaxActiveBlocksPerMultiprocessor. Essa função prediz a ocupância (dada pela quantidade de blocos ativos máximos) em termos do tamanho do bloco e uso de memória compartilhada de um kernel. Para calcular a ocupância em termos de porcentagem, podemos utilizar a fórmula seguinte:

$$Ocup ancia = \frac{\left(\frac{maxActiveBlock*blockSize}{props.warpSize}\right)}{\left(\frac{props.maxThreadsPerMultiProcessor}{props.warpSize}\right)}$$

Eq. 3.2

Onde as variáveis *props.warpSize* e *props.maxThreadsPerMultiProcessor* podem ser obtidas através da biblioteca *cudaGetDeviceProperties* da Nvidia.

#### 4.2. Naive Puro e Melhorado